EUV-Lithografie schrumpft Prozessoren-Leiterbahnen

Dieser Artikel ist älter als ein Jahr!

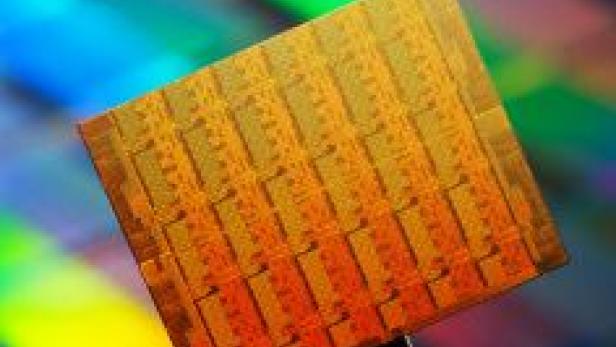

Nach wiederholten Verschiebungen ist die EUV-Lithografie jetzt reif für einen Einsatz in der Produktion, wie nextbigfuture berichtet. Die Technik, die extrem kurzwellige UV-Strahlung (13,5 nm Wellenlänge) nutzt, um in Zusammenarbeit mit lichtempfindlichen Chemikalien die Leiterbahnen auf Chips zu ätzen, soll es in den nächsten Jahren ermöglichen, bisher unerreicht kleine Strukturen auf Halbleitern zu realisieren.

Die nächsten Meilensteine sind Strukturen mit einer Größe von zehn beziehungsweise sieben Nanometer. Prozesse für beide Schritte lassen sich mit EUV-Lithografie realisieren. Für den Sprung auf die Fünf-Nanometer-Stufe sind allerdings noch Verbesserungen an der Technologie notwendig. "Wir haben 12 bis 18 Monate, um hier eine große Verbesserung zu erreichen. Im kommenden Jahr wird die Industrie aber viele Wafer verarbeiten, das wird bei der Entwicklung helfen", sagt ein Sprecher des Prozessentwicklers ASML.

Bei ASML gibt es Pläne , die Betriebszeiten der EUV-Anlagen von heute 75 auf 90 Prozent zu steigern. Zudem muss noch eine Abdeckung entwickelt werden, mit der eine Verunreinigung der Wafer verhindert werden kann. Die Geschwindigkeit der Anlagen soll von derzeit 145 Wafern pro Stunde bis 2020 auf 155 gesteigert werden. Der Chipproduzent TSMC erzeugt bereits Sieben-Nanometer-Chips. Im Jahr 2019 sollen bereits mehrere Firmen mit EUV-Anlagen produzieren. Samsung plant für 2019 bereits Sechs- und sogar Fünf-Nanometer-Chips. Auch TSMC will 2019 in den Fünf-Nanometer-Bereich vorstoßen.

Kommentare